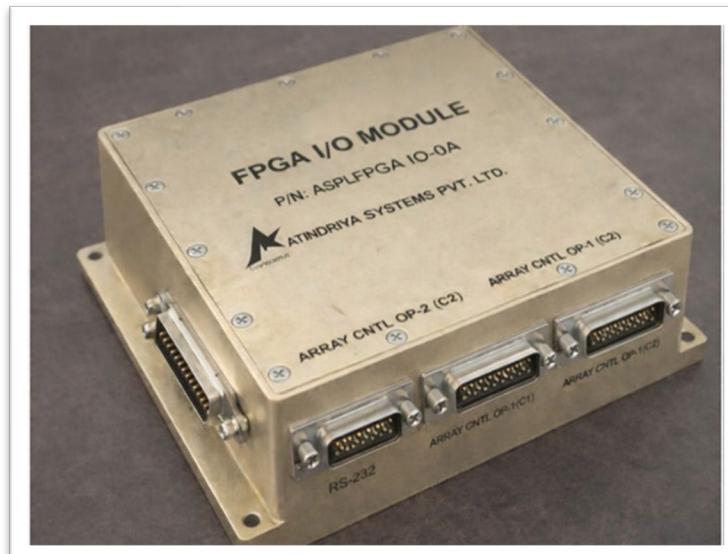

# ASPL-FPGA IO- 0A

## FPGA-Based Scalable Digital I/O Module

Atindriya's FPGA-based Digital I/O Module (ASPLFPGA IO-0A) is a standardized, high-density digital I/O building block designed for large Automated Test Equipment (ATE) platforms requiring thousands of deterministic I/O lines. Developed with a fully indigenous FPGA architecture and proven in multiple defence test systems supplied to DRDO Labs (CABS, LRDE etc), the module enables linear scalability from hundreds to few thousands digital I/O lines by simple replication, without any change to the base hardware design. With fixed interfaces, configurable firmware, and distributed control architecture, the solution offers a robust, long-term alternative to proprietary I/O cards for radar, avionics, EW, and missile test applications.

### Features

- High-speed serial LVDS control interface

- Local serial-to-parallel decoding

- Reduced cabling and lower BOM cost

- Fast inter-module switching

- Parallel operation across multiple modules

- Scalable and modular design

| Key Parameters             |                                         |

|----------------------------|-----------------------------------------|

| <i>FPGA Part Number</i>    | <b>XC7A200T-1FFG1156I – AMD- Xilinx</b> |

| <i>Logic Cells</i>         | <b>215,360</b>                          |

| <i>Block RAM</i>           | <b>13,455,360 bits</b>                  |

| <i>Configuration Flash</i> | <b>256Mb –QSPI Memory</b>               |

| <i>User I/O pins</i>       | <b>400( TTL I/O's)</b>                  |

| <i>LVDS interface</i>      | <b>10 no's</b>                          |

| <i>RS422 interface</i>     | <b>5 no's</b>                           |

### Environmental:

- Temperature: -20<sup>0</sup>C to +55<sup>0</sup>C

- Storage Temperature: -40<sup>0</sup>C to + 85<sup>0</sup>

### Outline Drawing:

# ASPL-FPGA IO- 0A

## FPGA-Based Scalable Digital I/O Module

This device provides sufficient logic resources, high-speed I/O capability, and deterministic performance required for real-time control and parallel signal distribution.

The FPGA I/O Module is a distributed control module designed for high-speed, low-latency I/O control applications. The module minimizes cabling and system cost by utilizing high-speed serial LVDS interfaces.

### Interfaces

|          |                         |

|----------|-------------------------|

| RS-232   | : 1 port                |

| RS-422   | : 1 port                |

| LVDS     | : 10 differential pairs |

| TTL I/Os | : 400                   |

| SL NO | PARAMETER                                          | SPECIFICATIONS                          |

|-------|----------------------------------------------------|-----------------------------------------|

| 1     | <i>Model no</i>                                    | <i>ASPLFPGA IO-0A</i>                   |

| 2     | <i>FPGA Part Number</i>                            | <i>XC7A200T-1FFG1156I – AMD- Xilinx</i> |

| 3     | <i>Logic Cells</i>                                 | <i>215,360</i>                          |

| 4     | <i>Block RAM</i>                                   | <i>13,455,360 bits</i>                  |

| 5     | <i>Configuration Flash</i>                         | <i>256Mb –QSPI Memory</i>               |

| 6     | <i>User I/O pins</i>                               | <i>400( TTL I/O's)</i>                  |

| 7     | <i>LVDS Pairs</i>                                  | <i>10 no's</i>                          |

| 8     | <i>Operating Temperature</i>                       | <i>-20°C to +55°C</i>                   |

| 9     | <i>Connector Type</i>                              | <i>D Type / Circular</i>                |

| 10    | <i>9-pin Debug connector</i>                       | <i>J-Tag ,RS232 ,RS422 ports</i>        |

| 11    | <i>Unit Dimensions *</i>                           | <i>L*W*H(120*120*60mm)</i>              |

|       | *Varies with connector type and Mounting Structure |                                         |

# ASPL-FPGA IO- 0A

## FPGA-Based Scalable Digital I/O Module

Previous Projects / Subsystems employed this IO Module:

**Project:** MySIR Test RIG

**End Customer:** CABS – DRDO

**Purpose :** To control 0.5-18GHz Co-Axial Switches in RWR Switch Matrix

**Project:** AEW&C Primary Radar Testing

**Customer:** LRDE – DRDO and CABS - DRDO

**Purpose :** To control 32 Channel 6-bit Phase Shifter and 32 Channel 6-Bit Attenuator

**Parameters are subject to change. For more information:**

Atindriya Systems, 3rd Floor, Chennamma layout, Seetharampalya, Whitefield, Bengaluru, Karnataka 560048

Phone: 9902202006, [sales@atindriya.co.in](mailto:sales@atindriya.co.in)